华之晶本文旨在深入剖析应用于显示屏的SPI接口,从底层协议的时序细节出发,追踪数据从主控MCU到屏幕像素的完整路径,并探讨驱动IC的内部架构与性能瓶颈,为嵌入式系统工程师提供一份全面的技术参考。

一、引言:SPI在显示领域的角色定位

在嵌入式系统中,SPI(Serial Peripheral Interface)因其引脚占用少、协议简单而被广泛采用。当它作为显示屏的控制接口时,其角色远不止一个简单的串行总线。它是一条承载着指令、参数和海量像素数据的生命线。要真正掌握SPI显示屏的驱动,必须深入理解其协议机制、数据流特性和驱动IC的内部工作原理。

二、协议层核心:SPI模式与DCX仲裁机制

SPI通信的基石是时钟同步,由时钟极性(CPOL)和时钟相位(CPHA)两个参数定义,组合成四种标准模式。

CPOL = 0: SCLK空闲状态为低电平。

CPOL = 1: SCLK空闲状态为高电平。

CPHA=0:在时钟的领先边沿(leading edge)采样数据

CPHA=1:在时钟的滞后边沿(trailing edge)采样数据

[常见TFT驱动IC(如ILI9341、ST7735、ST7789)仅支持Mode 0(CPOL=0, CPHA=0)。]

显示屏驱动IC(如ILI9341, ST7735)在其数据手册中会明确规定其支持的SPI模式。主控MCU的SPI控制器必须配置为完全匹配的模式,否则将导致数据采样错误,通信失败。这是驱动初始化的第一步,也是最关键的一步。

DCX(Data/Command Control)的仲裁角色:

DCX引脚(有时标记为D/C或A0)是SPI显示接口中一个至关重要的仲裁信号,它定义了总线上传输内容的性质。其工作机制如下:

DCX = 0 (低电平):总线上的字节流被驱动IC解释为指令。这些指令用于配置屏幕的工作状态,如设置显示窗口、睡眠模式、伽马校正等。

DCX = 1 (高电平):总线上的字节流被驱动IC解释为数据。这通常是要写入显存(GRAM)的像素颜色值。

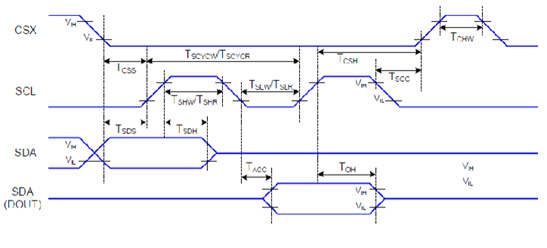

一个典型的写操作时序如下:

主控拉低 CS,选中屏幕。

主控拉低 DCX。

主控通过SPI发送一个字节的指令码(例如 0x2A,设置列地址)。

(可选)主控继续发送该指令所需的参数(此时DCX保持低电平)。

主控拉高 DCX。

主控通过SPI发送大量的像素数据。

对DCX引脚的精确、时序无误的控制,是驱动显示屏正常工作的核心前提。

三、数据流剖析:通用指令集与像素渲染过程

为了在屏幕上绘制一个特定区域(如一个矩形或一个字符),主控MCU需要通过SPI接口向驱动IC发送一系列标准化的指令。这个过程通常遵循一个通用的“三步走”模式,尽管具体指令码可能因驱动IC型号而异,但其逻辑是相通的。

让我们以绘制一个矩形为例,来完整追踪这个通用的数据流:

1. 设置水平显示窗口

DCX=0,MCU首先发送 “设置列地址窗口”指令。这是一个母集指令,其功能是定义显示区域的左右边界。

DCX=0,紧随其后,MCU发送该指令所需的参数。通常是四个字节:起始列地址的高字节、起始列地址的低字节、结束列地址的高字节和结束列地址的低字节。驱动IC接收到这些参数后,就知道了后续操作的水平范围。

2. 设置垂直显示窗口

DCX=0,MCU接着发送 “设置页地址窗口”指令。这个指令的功能是定义显示区域的上下边界。

DCX=0,同样,MCU发送其对应的参数:起始行地址的高字节、起始行地址的低字节、结束行地址的高字节和结束行地址的低字节。

至此,一个由 (起始列, 起始行) 到 (结束列, 结束行) 定义的矩形窗口就在驱动IC内部建立好了。

3. 开始写入像素数据

· 写入显存(GRAM) DCX=0,发送“写入显存”指令(ILI9341为0x2C,ST7789/ST7735为0x2C RAMWR)。 立即将DCX拉高,后续连续发送的全部字节都会被驱动IC自动顺序写入之前设置好的窗口内对应的GRAM地址,无需额外指令。

驱动IC会自动将这些接收到的像素数据,依次填充到刚刚设置的GRAM窗口中,最终在屏幕上呈现出我们想要的矩形。

四、性能瓶颈与架构优化

SPI接口的串行特性带来了天然的带宽限制,这成为其在高性能显示应用中的主要瓶颈。

1. 带宽计算:

SPI的有效数据传输速率由时钟频率决定。例如,在40MHz的SCLK下,理论带宽为 40MHz / 8 = 5MB/s。对于一块320x240分辨率、RGB565格式的屏幕,全屏刷新所需的数据量为 320 * 240 * 2 = 153,600 字节。理论上的最高刷新率约为 5MB/s / 153.6KB ≈ 32.5 FPS(以上为理想计算,实际受指令开销、CS/DCX切换、MCU SPI FIFO深度等影响,刷新率通常只有理论值的50~70%。)。这个速率对于动态UI和简单动画尚可,但无法满足视频播放的需求。

2. CPU负载与DMA:

在没有硬件加速的情况下,CPU需要通过轮询或中断的方式,将每一个字节的像素数据写入SPI数据寄存器。在进行全屏刷新时,CPU将被完全占用,无法处理其他任务。

DMA(Direct Memory Access)是解决此问题的关键。DMA控制器可以在没有CPU干预的情况下,将数据从内存(如Frame Buffer)直接搬运到SPI外设的数据寄存器。CPU只需发起DMA传输请求,之后即可处理其他任务,极大地提升了系统效率。

3. 高级接口:QSPI

它使用4条数据线(IO0, IO1, IO2, IO3)在时钟的每个边沿传输4位数据,从而将理论带宽提升至标准SPI的4倍。这使得驱动更高分辨率、更高刷新率的屏幕成为可能。

4. 9-bit SPI

9-bit SPI是标准SPI协议的一种非标准扩展,其数据帧长度为9位。其核心价值在于利用多出的第9位作为标志位,用以区分后续8位数据是指令还是数据。这种设计最经典的应用是在一些显示屏控制器(如ILI9341)中,能够省去专门的DCX(数据/命令选择)引脚,从而简化硬件布线、节省宝贵的I/O资源。实现上,它依赖于MCU的硬件支持或通过软件模拟。尽管如今引脚充足的MCU使其应用减少,但9-bit SPI作为一种经典的通信技巧,在嵌入式系统设计中仍具有重要参考价值。

五、驱动IC内部架构揭秘

显示屏本身只是一个被动矩阵,其智能完全来自于内部的驱动IC。理解驱动IC的架构,是理解SPI显示接口的最后一环。

指令译码器与控制逻辑: 接收并解析SPI总线上的指令和参数,配置驱动IC的各个功能模块。

GRAM(图形RAM): 这是驱动IC的核心存储单元。它是一块片上内存,用于存储当前一帧的图像数据。

有GRAM的架构: CPU通过SPI将一帧图像写入GRAM后即可脱身。驱动IC内部的时序控制器会自动从GRAM读取数据,并持续刷新屏幕,保持图像稳定。这是现代TFT驱动IC的主流架构。

极少数被动矩阵OLED(如大尺寸的部分产品)没有GRAM(SPI接口,一般都是有GRAM的,部分QSPI的接口可能没有。具体情况具体分析),需要主机持续刷新(现代有源矩阵OLED和所有主流TFT驱动IC均内置完整GRAM): 驱动IC没有足够大的GRAM。MCU必须持续不断地通过SPI发送像素数据来维持图像,一旦停止,屏幕内容就会消失。这种架构对CPU的实时性要求极高。

时序控制器与源/栅极驱动器: TCON从GRAM中读取像素数据,并将其转换为驱动LCD或OLED像素矩阵所需的具体时序信号和电压信号,最终控制每个像素点的亮度和颜色。

六、核心特点和应用

1、SPI接口核心特点(对比RGB/I2C)

(1) 硬件与成本:引脚仅4-6根,连接简单,无需专用控制器,比RGB接口(16-24根线+专用控制器)更省资源、成本更低;虽比I2C(2根线)多引脚,但扩展多从机更灵活。

(2)传输性能:全双工通信,速率远高于I2C(10倍以上),能快速更新显示内容;虽不及RGB接口(并行传输,高刷新率/分辨率适配),但满足中小屏基本需求。

(3)适配性:协议简洁、编程易实现,兼容多数MCU、FPGA,适配性强,兼顾性能与易用性。

2、核心应用场景

聚焦中小尺寸(1-5英寸)、轻量化显示需求,优先用于:

- 便携式设备(智能手表、运动手环、手持检测仪);

- 工业控制/物联网终端(小型操作面板、传感器数据屏);

- 消费电子配件(蓝牙音箱、小型家电显示屏);

- 对成本敏感、空间受限,且无需超高清/高刷新率的批量生产产品。

七、结论

SPI接口显示屏是一个典型的软硬件结合系统。其外部的SPI接口定义了通信的物理层和链路层,而内部的驱动IC则实现了数据处理、存储和显示控制的核心功能。深入理解SPI模式、DCX机制、数据流过程以及驱动IC的GRAM架构,是高效、稳定地驱动显示屏的根本。只有掌握了这些底层技术细节,工程师才能在面对性能优化、功耗控制和疑难杂症时,游刃有余。

在数字时代,LCD屏幕无处不在,从手机和平板电脑到电视和显示器。尽管LCD技术已经相当成熟,提供了成本效益高且性能稳定的显示解决方案,但在其生命周期中,用户可能会遇到各种显示问题。本文深入探讨LCD显示屏的常见不良现象,分析其原因,并提供针对性的解决方案,帮助用户和技术人员更好地理解和维护他们的设备。

TFT-LCD屏可视为两片玻璃基板中间夹着一层液晶,上层的玻璃基板是与彩色滤光片(ColorFilter)、而下层的玻璃则有晶体管镶嵌于上。当电流通过晶体管产生电场变化,造成液晶分子偏转,藉以改变光线的偏极性,再利用偏光片决定像素(Pixel)的明暗状态。此外,上层玻璃因与彩色滤光片贴合,形成每个像素(Pixel)各包含红蓝绿三颜色,这些发出红蓝绿色彩的像素便构成了皮肤上的图像画面。

深圳市华之晶科技有限公司(SinoCrystal)是一家专注于显示屏研发、生产与销售的国家级高新技术企业。多年深耕工业级显示器件领域,产品以稳定可靠、适配严苛环境著称。

AI 机器人的爆火不仅源于算法突破,其搭载的屏幕更是暗藏诸多技术门道,绝非普通平板屏可比。为规避恐怖谷效应,屏幕需 120Hz 以上高刷新率、5ms 内低响应时间;还得具备工业级品质,MTBF 达 5 万小时以上,宽温技术适配 - 30℃至 80℃环境,抗震动设计保障稳定;户外款更是标配 1000nits 以上高亮屏,兼顾散热与功耗。这块屏幕是机器人交互核心,也是连接物理与数字世界的窗口,随着服务机器人市场增长,其专用屏也迎来全新蓝海。

在精密电子产品的物流运输中,包装不仅是产品的“外衣”,更是品质的“护城河”。尤其是对于显示屏这类易碎且对环境要求极高的产品,包装的科学与严谨直接关系到最终交付的完好率。

市面上最常见的触摸屏按结构划分,主要分为电阻式触摸屏和电容式触摸屏两大类。它们各自拥有独特的工作原理和特性,适用于不同的场景。我们将客观地从核心原理、外观显示、用户体验、耐用性及应用场景等多个维度,为您深入剖析电阻屏与电容屏的区别,助您为产品选择最合适的交互方案。